- Tektronix announces a PCI Express 5.0 (Base and CEM) transceiver and reference clock solution, providing CEM (Card Electromechanical) connection systems for pre-conformity testing.

- This solution, the result of collaboration between Tektronix and Anritsu, enables receiver verification, in addition to a suite of tools for testing transmitters and reference clocks.

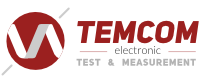

- The PCIe solution is designed for Tektronix’s DPO/MSO70000SX/DX series oscilloscopes.

The bandwidth of the PCI Express serial bus doubles every three years. PCI Express 5.0 specification now enables speeds up to 128 GB/s. This will increase further as PCI-SIG, the standards body for peripheral I/O components for data transfer, will release the PCI EXPRESS 6.0 (256 GB/s) specification in 2021, which includes PAM4 multi-level pulse-amplitude modulation technology.

With the adoption of the PCIe 5.0 interface, new issues are emerging regarding the traditional test and measurement procedures of silicon-level validation and CEM compliance testing according to the PCI-SIG specification. “We are the first company to offer CEM test solutions that meet the requirements of the PCIe Gen5 standard,” said Chris Witt, vice president and general manager of Tektronix.

Tektronix’s PCIe 5.0 testing and debugging solutions help ensure that designs meet the requirements of the new standards. The U.S. manufacturer’s PCI Express 5.0 transceiver and reference clock solution meets the requirements and evolutions of the 5.0 Base specification, 5.0 CEM specification, and 5.0 test specifications.

Key features include:

• PCI EXPRESS 5.0 (32 GT/s) automated Base & CEM Transmitter solution running on DPO700000SX series real time oscilloscope and MP1900A Signal Quality Analyser-R series (BERT) from Anritsu

• New Receiver automation software from Tektronix with algorithms for stressed eye calibration at 32 GT/s & 16GT/s.

• Tool support including SigTest Phoenix with parallelized processing to reduce overall test time

• Multiple form factors (M.2 & U.2) and Clocking Architectures (CC, SRNS, SRIS)

• Follows real time evolution of the 5.0 Base specification with 32 GT/s uncorrelated jitter and pulse width jitter measurements implemented to optimize A/D range and minimize noise

• Addresses the increasing challenges of 100 MHz reference clock jitter and signal integrity measurements through full integration with the Silicon Labs “PCIe Clock Jitter” tool and Tektronix’s DPOJET tool

• Pre compliance test fixtures for PCIe 5.0 CEM testing.