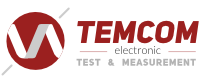

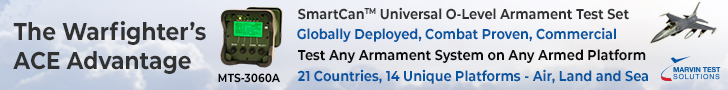

- Teledyne LeCroy announces the CrossSync PHY family of interposers and software options that provide the link between an oscilloscope and a PCI Express protocol analyzer.

- This solution enables the optimization of PCI Express (PCIe) interface test procedures and the analysis of signal and protocol information from a single visualization interface.

During testing and debugging of PCIe interfaces, a protocol analyzer allows protocol messages between components to be visualized over a relatively long period of time. An oscilloscope must also be used to measure the electrical characteristics of the PCIe links at the physical layer with high resolution. However, capturing protocol messages with oscilloscopes is not possible because these instruments do not have enough memory before the protocol event occurs.

For this reason, when testing a device with a PCI Express interface, engineers must use the two instruments separately in completely different configurations. By connecting the oscilloscope to the protocol analyzer using Teledyne LeCroy’s new CrossSync PHY interconnection system combining probes and software options, engineers can now test PCIe links using a single test system.

“Engineers attempting to integrate PCIe interfaces have repeatedly told us of the problems associated with integrating this complex technology and their frustration at not being able to visualize and correlate the physical and protocol layers from a single visualization interface. Our new CrossSync PHY technology does just that,” said Kevin Prusso, Vice President and General Manager of Teledyne LeCroy.

“The correlation between protocol and electrical signal events has been a sore point in our debugging sessions,” said Srajit Singh, Product Validation Architect at Intel. “This solution is exactly what we need. We believe it will speed up our debugging efforts when dealing with complex PCIe issues at the borderline between electrical and functional domains. »